Для того чтобы дальше разбираться с TWI модулем, нужно ознакомиться с его регистрами, и сейчас нам придется проделать эту нудную работу. Разбор регистров будет вестись на примере микроконтроллера atmega16. В других микроконтроллерах возможны небольшие отличия.

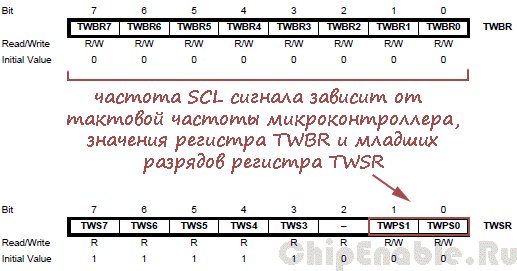

Регистр скорости передачи TWBR (TWI Bit Rate Register)

Любой аппаратный модуль, реализующий интерфейс (SPI, UART, TWI, USB), имеет регистры задающие скорость передачи данных. В TWI модуле эту функцию выполняет регистр TWBR и два младших разряда статусного регистра TWSR - TWPS1 и TWPS0.

Под скоростью передачи в данном случае подразумевается частота SCL сигнала, когда микроконтроллер работает в режиме ведущего устройства (мастера). В режиме ведомого (слейва) микроконтроллер "получает" SCL сигнал извне - от другого ведущего устройства. (Тактовая частота микроконтроллера в этом случае, должна быть больше частоты внешнего SCL сигнала минимум в 16 раз.)

Тактовая частота микроконтроллера, частота SCL сигнала и значение регистров TWBR и TWSR связаны следующим соотношением:

F_scl = F_cpu/(16 + 2* TWBR* 4^TWPS)

Здесь значок ^ это возведение в степень. TWPS - значение младших разрядов регистра TWSR, а TWBR- значение, содержащееся в этом регистре.

Из этой формулы можно выразить значение TWBR:

TWBR = ((F_cpu/F_scl) - 16)/(2*4^TWPS)

Рассмотрим пример расчета.

Тактовая частота микроконтроллера 16 МГц, нужно задать частоту SCL сигнала 100 кГц. Допустим, мы выбрали нулевое значение для битов TWPS1 и TWPS0. Тогда значение для TWBR будет равно:

TWBR = ((16000000/100000) - 16)/(2*4^0) = 72

Довольно просто.

Чем руководствоваться при выборе частоты SCL сигнала?

1. Возможностями устройства, с которым производится обмен по I2C. Например, микросхема часов реального времени DS1307 поддерживает частоту SCL сигнала только до 100 кГц.

2. Тактовой частотой микроконтроллера. Она накладывает естественное ограничение на возможность задания максимальной частоты. Это очевидно.

3. Электрическими характеристиками сети I2C. При большом количестве устройств и большой протяженности сети, передача данных на максимальной скорости может оказаться невозможной - сигналы будут искажаться из-за паразитной емкости сети или помех. Номиналы подтягивающих резисторов тоже влияют на максимальную частоту. Об этом можно прочитать в даташите atmega16 в разделе Two-wire Serial Interface Characteristics.

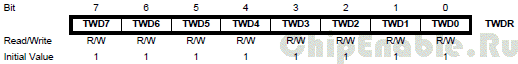

Регистр данных TWDR (TWI Data Register)

Функции регистра данных очевидны. В него мы помещаем то, что хотим передать и забираем то, что получили с шины. Когда все это нужно делать, будет понятно в практической части.

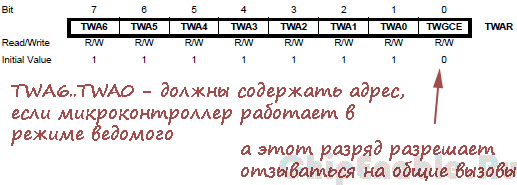

Регистр адреса TWAR (TWI Address Register)

Микроконтроллер может выполнять функции как ведущего, так и ведомого устройства. Естественно по очереди, а не одновременно.

Если микроконтроллер выступает в роли ведомого, ему необходим адрес, на который он будет "отзываться". Регистр TWAR и предназначен для хранения 7-и разрядного адреса. Младший разряд (TWGCE) этого регистра разрешает/запрещает микроконтроллеру отзываться на общие вызовы, то есть на пакеты с адресом 0x00.

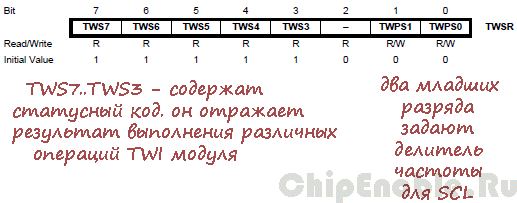

Статусный регистр TWSR (TWI Status Register)

Статусный регистр TWSR отражает состояние TWI модуля и двухпроводной шины, а также содержит разряды, задающие коэффициент деления частоты SCL сигнала. В самом начале мы об этом говорили.

Биты TWS7.. TWS3 содержат статусный код. Биты доступны только для чтения, статусный код устанавливается TWI модулем аппаратно, после выполнения различных операций. Например, формирование состояния СТАРТ, передачи пакета данных и так далее. По значению статусного кода можно судить о результате операции. Выполнилась ли она успешно или нет.

Кодов много, поэтому будем рассматривать их в практической части. В топорном варианте работы с TWI модулем их можно игнорировать, но тогда надежность программы будет заведомо низкая.

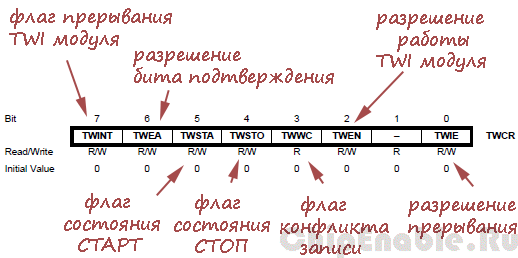

Регистр управления TWCR (TWI Control Register)

TWCR - самый важный регистр TWI модуля. Много разрядов, каждый отвечает за отдельную функцию, поэтому я оставил его на десерт.

TWINT(TWI Interrupt Flag) - флаг прерывания TWI модуля. Этот бит устанавливается аппаратно, когда TWI модуль завершает текущую операцию (формирование состояния СТАРТ, передачи адресного пакета и так далее). При этом если установлен бит глобального разрешения прерываний (бит I регистра SREG) и разрешены прерывания TWI модуля, то вызывается соответствующий обработчик.

Бит TWINT очищается программно, записью единицы. При выполнении обработчика прерывания этот бит не сбрасывается аппаратно, как в других модулях. Сброс флага TWINT запускает работу TWI модуля, поэтому все операции с регистром данных, статуса или адреса, должны быть выполнены до его сброса.

Пока бит TWINT установлен, на линии SCL удерживается низкий уровень.

TWEA (TWI Enable Acknowledge Bit) - разрешение бита подтверждения. Если бит TWEA установлен в 1, TWI модуль формирует сигнал подтверждения (ACK), когда это требуется. А требуется это в трех случаях: ведущее или ведомое устройство получило байт данных, ведомое устройство получило общий вызов, ведомое устройство получило свой адрес.

TWSTA (TWI START Condition Bit) - флаг состояния СТАРТ. Когда этот бит устанавливается в 1, TWI модуль проверяет не занята ли шина и формирует состояние СТАРТ. Если шина занята, он будет ожидать появления на ней состояния СТОП и после этого выдаст состояние СТАРТ. Бит TWSTA должен быть очищен программно, когда состояние СТАРТ передано.

TWSTO (TWI STOP Condition Bit) - флаг состояния СТОП. Когда этот бит устанавливается в 1 в режиме ведущего, TWI модуль выдает на шину состояние СТОП и сбрасывает этот бит. В режиме ведомого установка этого бита может использоваться для восстановления после ошибки. При этом состояние СТОП не формируется, но TWI модуль возвращается к начальному не адресованному состоянию.

TWWC (TWI Write Collision Flag) - флаг конфликта записи. Этот флаг устанавливается аппаратно, когда выполняется запись в регистр данных (TWDR) при низком значении бита TWINT. То есть когда TWI модуль уже выполняет какие-то операции.

Флаг TWWC сбрасывается аппаратно, когда запись в регистр данных выполняется при установленном флаге прерывания TWINT.

TWEN (TWI Enable Bit) - бит разрешения работы TWI модуля. Когда бит TWEN устанавливается в 1, TWI модуль включается и берет на себя управление выводами SCL и SDA. Когда бит TWEN сбрасывается, TWI модуль выключается.

TWIE (TWI Interrupt Enable) - разрешение прерывания TWI модуля. Когда бит TWIE и бит I регистра SREG установлены в 1 - прерывания модуля TWI разрешены. Прерывания будут вызываться при установке бита TWINT.

На этом все. Продолжение следует. Вступаем в группу в контакте.

Comments

4^0 = 1

4^1 = 4

4^2 = 16

4^3 = 64

RSS feed for comments to this post